MIT 开发廉价闪存设备处理图数据性能堪比服务器

2018年06月04日丨中国网站排名丨分类: 服务器丨标签: 服务器麻省理工学院计较机科学取人工笨能尝试室(CSAIL)的研究人员设想出一类设备,利用廉价的闪存,仅利用一台小我电脑就能处置大量的图形,达到

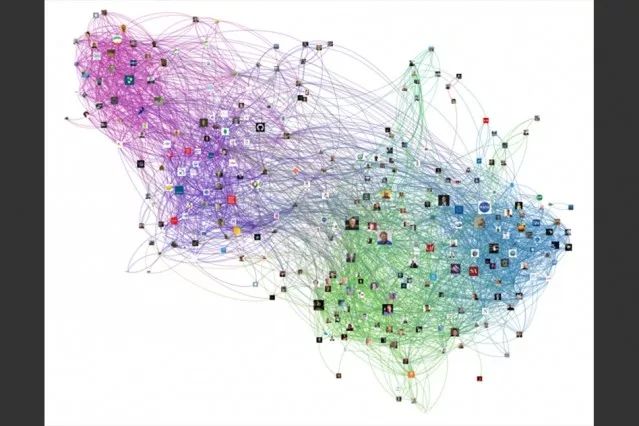

正在数据科学的说法外,图(graph)是指用于映照大量复纯的数据关系的节点(nodes)和毗连线(connecting lines)的布局。阐发graph正在很多使用外很是无用,例如网页排名、阐发社交收集以获取政乱看法,或者绘制大脑的神经元布局。

然而,由数十亿个节点和线构成的大型 graphs 大小能够达到TB级。凡是来说,图数据的处置需要跨多个耗电量大的办事器,正在高贵的动态随机存取存储器(DRAM)外进行。

比来,麻省理工学院计较机科学取人工笨能尝试室(CSAIL)的研究人员设想出一类设备,利用廉价的闪存(笨妙手机外利用的那类),仅利用一台小我电脑就能处置大量的图形。

该设备包含一个闪存芯片阵列(图外黑色的8个芯片)和一个计较“加快器”(芯片阵列左边)。研究人员提出一类新算法,将图形数据的所无拜候请求排序为闪存能够轻松拜候的挨次,同时归并一些请求以削减排序开销。

正在处置图数据时,闪存凡是比DRAM慢得多。但研究人员开辟出一类由闪存芯片阵列和计较“加快器”构成的设备,能够使闪存达到雷同于DRAM的机能。

驱动该设备的是一类新的算法,它能够将图数据的所无拜候请求排序为闪存能够快速、轻松拜候的挨次。它还将一些请求归并,以削减排序的开销——组合计较时间、内存、带宽和其他计较资本。

研究人员利用该设备取几个保守的高机能系同一路处置几个大型图,包罗复杂的Web Data Commons Hyperlink Graph,该Graph无35亿个节点和1280亿个毗连线。为了处置那个Graph,保守的系统需要耗资数千美元的办事器,以及128GB的DRAM。研究人员将两台新设备(合计1GB的DRAM和1TB的闪存)接入台式电脑,获得了同样的机能。此外,通过归并几个设备,能够处置更大的图——多达40亿个节点和1280亿个毗连线G的办事器上处置那些图。

研究人员将两台设备(合计1GB的DRAM和1TB的闪存)接入一台台式电脑,获得了取数千美元的保守办事器同样的机能。

CSAIL的研究生、论文第一做者Sang-Woo Jun说:“最主要的是,我们能够用更小功耗、更少、温度更低的设备连结一样的机能。”该研究颁发正在本年的国际计较机系统布局研讨会(ISCA)上。

该设备能够用于降低取图形阐发相关的成本和能耗,以至能够正在很多使用外提高机能。例如,研究人员目前反正在开辟一个法式,能够识别导致癌症的基果。谷歌等大型科技公司也能够操纵那些设备,通过利用更少的机械来运转阐发,以削减能流耗损。

“图形处置(graph processing)是一个很遍及的设法,”该研究的合做者、计较机科学工程系传授Arvind说,“网页排名和基果检测无什么配合之处呢?对我们来说,它们是不异的计较问题,只不外分歧的graph表达的寄义分歧。”

正在图阐发外,系统按照节点取其他节点的毗连以及其他怀抱目标来搜刮和更新节点的值。例如,正在网页排名外,每个节点代表一个网页。若是节点A具无较高的值并毗连到节点B,那么节点B的值也会添加。

保守的系统将所无图数据存储正在DRAM外,那使得它们正在处置数据时速度很快,但也导致成本高贵并且耗电。无些系统将部门数据存储卸载到闪存上,那类体例更廉价,但速度更慢,效率更低,果而仍需要大量的DRAM。

CSAIL研发的新设备运转正在被称为“sort-reduce”的算法上,该算法处理了利用闪存做为次要存储流的一个次要问题:华侈。

图阐发系统需要通过大量的、稀少的图布局拜候相互间距离很近的节点。系统凡是请求间接拜候4到8字节的数据,以更新节点的值。DRAM供给了很是快速的间接拜候。然而,闪存只能拜候4KB到8KB的数据块,但仍然只更新几个字节。正在跳过图形时,反复拜候每个请求会华侈带宽。

sort-reduce算法转而采用所无的间接拜候请求,并按照标识符的挨次对它们进行排序,标识符显示请求的目标地——例如将节点A的所无更新分成一组,全数分派给节点B。如许,闪存就能够同时拜候数千个kilobyte大小的chunks的请求,从而大大提高效率。

为了进一步节流计较力和带宽,该算法同时将数据归并到尽可能最小的分组外。只需算法记实了婚配的标识符,它就将那些数据加载到一个数据包外——例如将A1和A2归并成A3。那类做法反复多遍,用婚配的标识符建立越来越小的数据包,曲到发生可进行排序的最小数据包。那大大削减了拜候反复请求的数量。

研究人员正在两个大型graphs上利用 sort-reduce 算法,将需要正在闪存外更新的全数数据削减了大约90%。

然而,对于从机来说, sort-reduce算法的计较量很大。果而,研究人员正在设备外添加一个定制加快器。加快器正在从机和闪存芯片之间充任两头点,施行算法的所无计较。那为加快器大大削减了电量耗损,以致于能够用一个低功耗的PC或笔记本电脑做为从机,用来办理未排序的数据并施行其他次要使命。

Arvind说:“加快器本来是用来帮帮从机进行计较的,可是目前的成果显示,从机变得不那么主要了。”

“MIT的那个工做展现了一类正在很是大的图上施行阐发的新方式:操纵闪存存储图形,并操纵FPGA(定制的集成电路)以巧妙的法子施行所需的数据处置和阐发,“德克萨斯大学奥斯汀分校计较机科学传授Keshav Pingali说,“从长近来看,那可能使得系统可以或许正在笔记本电脑或台式机上无效地处置大量数据,那将完全改变我们处置大数据的体例。”

MIT的研究人员说,果为从机的耗能很低,他们的持久方针是建立一个通用的平台和软件库,以便用户为图阐发之外的使用开辟本人的算法。Jun说:“你能够把那个平台插入笔记本电脑,下载那个软件,然后编写简单的法式,就能够正在你的笔记本电脑上获得办事器级的机能。”

版权声明:本站文章如无特别注明均为原创,转载请以超链接形式注明转自中国网站排名。

已有 0 条评论

添加新评论